# Butterfly Microcontroller Handbook

HB4100-2.0

For performance characteristics, refer to the Butterfly Microcontroller Performance Supplement: Publication no. SP4578 (for Commercial grade specification) or SP4708 (for Industrial grade specification)

© Mitel Corporation 1998 Publication No.HB4100-2.0 Issue No.2.0 Rev.C March 1998

#### TECHNICAL DOCUMENTATION - NOT FOR RESALE. PRINTED IN UNITED KINGDOM

This publication is issued to provide information only which (unless agreed by the Company in writing) may not be used, applied or reproduced for any purpose no form part of any order or contract nor to be regarded as a representation relating to the products or services concerned. No warranty or guarantee express or implied is made regarding the capability, performance or suitability of any product or service. The Company reserves the right to alter without prior notice the specification, design or price of any product or service. Information concerning possible methods of use is provided as a guide only and does not constitute any guarantee that such methods of use will be satisfactory in a specific piece of equipment. It is the user's responsibility to fully determine the performance and suitability of any equipment using such information and to ensure that any ublication or data used is up to date and has not been superseded. These products ar not suitable for use in any medical products whose failure to perform may result in significant injury or death to the user. All products and materials are sold and services provided subject to the Company's conditions of sale, which are available on request. All brand names and product names used in this publication are trademarks, registered trademarks or tradenarks.

| TABLE OF CONTENTS    | i - viii |

|----------------------|----------|

| LIST OF FIGURES      | ix       |

| LIST OF TABLES       | xiii     |

| Document Conventions | xvii     |

# **Chapter 1 - Introduction**

| BUTTE   | ERFLY microcontroller overview 1-1                                                                                                                                                                                          |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.1.1   | Features 1-1                                                                                                                                                                                                                |

| Functio | onal Block Description 1-2                                                                                                                                                                                                  |

| 1.2.1   | BmILD Bus 1-2                                                                                                                                                                                                               |

|         | ARM7 Processor (ARM7) 1-2                                                                                                                                                                                                   |

|         | BmILD Broadcast Module (BBM) 1-3                                                                                                                                                                                            |

|         | Phase Locked Loop (PLL)                                                                                                                                                                                                     |

|         | Power Control (POCO)                                                                                                                                                                                                        |

| -       | Power-On Reset (POR)                                                                                                                                                                                                        |

|         | Programmable Peripheral Interface (PPI) 1-3                                                                                                                                                                                 |

|         | Memory/Peripheral Controller (MPC)                                                                                                                                                                                          |

| -       | Universal Asynchronous Receiver Transmitter (UART) 1-4                                                                                                                                                                      |

|         | Interrupt Controller (INTC)                                                                                                                                                                                                 |

|         | DMA Controller (DMAC)                                                                                                                                                                                                       |

|         | Timer/Counters (TIC)                                                                                                                                                                                                        |

|         | Watchdog Timer (WDOG) 1-5                                                                                                                                                                                                   |

| BUTTE   | ERFLY System Details 1-6                                                                                                                                                                                                    |

| 1.3.1   | System Address Map 1-6                                                                                                                                                                                                      |

| 1.3.2   | Address Map for internal I/O 1-7                                                                                                                                                                                            |

| 1.3.3   | System Clock Control 1-8                                                                                                                                                                                                    |

| 1.3.4   | System Reset 1-8                                                                                                                                                                                                            |

| 1.3.5   | System Bus Arbitration 1-8                                                                                                                                                                                                  |

| 1.3.6   | System Configuration Register 1-9                                                                                                                                                                                           |

| 1.3.7   | DMA 1-11                                                                                                                                                                                                                    |

| 1.3.8   | Interrupt Sources 1-12                                                                                                                                                                                                      |

| 1.3.9   | Timer Counter (TIC) configuration 1-14                                                                                                                                                                                      |

|         | 1.1.1<br>Function<br>1.2.1<br>1.2.2<br>1.2.3<br>1.2.4<br>1.2.5<br>1.2.6<br>1.2.7<br>1.2.8<br>1.2.9<br>1.2.10<br>1.2.11<br>1.2.12<br>1.2.13<br>BUTTH<br>1.3.1<br>1.3.2<br>1.3.3<br>1.3.4<br>1.3.5<br>1.3.6<br>1.3.7<br>1.3.8 |

# Chapter 2 - ARM7 Microprocessor

| 2.1 | Overvie                                                                                                               | ÐW                                                                                                                                                                                                                                                                                                                                                                                                           | 2-1                                                                                  |

|-----|-----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|

| 2.2 | Archite                                                                                                               | cture                                                                                                                                                                                                                                                                                                                                                                                                        | 2-2                                                                                  |

| 2.3 | Progra                                                                                                                | mmer's Model                                                                                                                                                                                                                                                                                                                                                                                                 | 2-3                                                                                  |

|     | 2.3.1<br>2.3.2<br>2.3.3<br>2.3.4<br>2.3.5<br>2.3.6<br>2.3.7<br>2.3.8<br>2.3.9<br>2.3.10<br>2.3.11<br>2.3.12           | Operating Mode Selection<br>Registers<br>Exceptions<br>FIQ<br>IRQ<br>Abort<br>Software Interrupt<br>Undefined Instruction Trap<br>Vector Summary<br>Exception Priorities<br>Interrupt Latencies<br>Reset                                                                                                                                                                                                     | . 2-3<br>. 2-7<br>. 2-7<br>. 2-8<br>. 2-8<br>. 2-9<br>. 2-9<br>2-10<br>2-10<br>2-11  |

| 2.4 | Instruct                                                                                                              | tion Set                                                                                                                                                                                                                                                                                                                                                                                                     | 2-12                                                                                 |

|     | 2.4.1<br>2.4.2<br>2.4.3<br>2.4.4<br>2.4.5<br>2.4.6<br>2.4.7<br>2.4.8<br>2.4.9<br>2.4.10<br>2.4.11<br>2.4.12<br>2.4.13 | Instruction Set Summary<br>The Condition Field<br>Branch and Branch with Link (B, BL)<br>Data Processing<br>PSR Transfer (MRS, MSR)<br>Multiply and Multiply-Accumulate (MUL, MLA)<br>Single Data Transfer (LDR, STR)<br>Block Data Transfer (LDM, STM)<br>Single Data Swap (SWP)<br>Software Interrupt (SWI)<br>Butterfly Coprocessor Support<br>Coprocessor Data Operations (CDP)<br>Undefined Instruction | 2-13<br>2-14<br>2-25<br>2-24<br>2-29<br>2-31<br>2-38<br>2-45<br>2-47<br>2-50<br>2-50 |

| 2.5 | Instruct<br>2.5.1<br>2.5.2<br>2.5.3<br>2.5.4<br>2.5.5<br>2.5.6<br>2.5.7<br>2.5.8                                      | tion Cycle Operations                                                                                                                                                                                                                                                                                                                                                                                        | 2-53<br>2-54<br>2-55<br>2-57<br>2-58<br>2-59<br>2-59                                 |

| 2.5.9  | Data Swap                                     | 2-62 |

|--------|-----------------------------------------------|------|

| 2.5.10 | Software Interrupt and Exception Entry        | 2-63 |

| 2.5.11 | Coprocessor Data Operation                    | 2-64 |

| 2.5.12 | Undefined Instructions and Coprocessor Absent | 2-65 |

| 2.5.13 | Unexecuted Instructions                       | 2-65 |

| 2.5.14 | Instruction Speed Summary                     | 2-65 |

|        |                                               |      |

# Chapter 3 - Diagnostic Broadcast (BBM)

| 3.1 | Overvie | Overview             |       |

|-----|---------|----------------------|-------|

|     | 3.1.1   | Diagnostic Broadcast | . 3-2 |

# Chapter 4 - Phase Locked Loop (PLL)

| 4.1 | Overv                                       | Overview 4-1                                                                                                                           |            |  |

|-----|---------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|------------|--|

| 4.2 | Desig                                       | Design features                                                                                                                        |            |  |

| 4.3 | Archit                                      | ecture                                                                                                                                 | 4-2        |  |

|     | 4.3.1<br>4.3.2                              | Interface Definitions<br>Operating Modes                                                                                               |            |  |

| 4.4 | PLL C                                       | Dperational Description                                                                                                                | 4-5        |  |

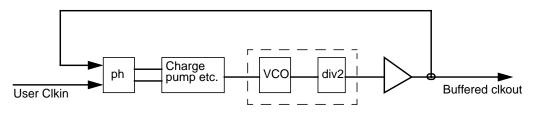

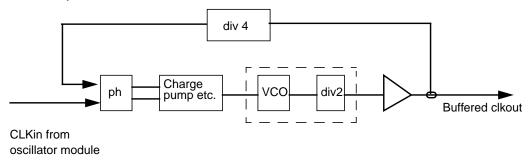

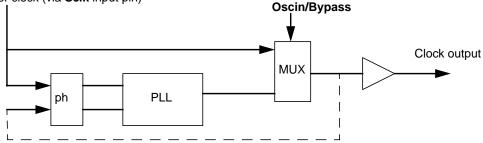

|     | 4.4.1<br>4.4.2<br>4.4.3<br>4.4.4            | PLL for User Clock input<br>PLL for Oscillator Clock input<br>PLL Clock bypass<br>PLL Operational details                              | 4-5<br>4-6 |  |

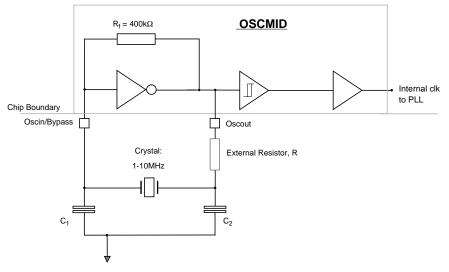

| 4.5 | Oscilla<br>4.5.1<br>4.5.2<br>4.5.3<br>4.5.4 | ator Operational Description<br>Pin Descriptions<br>Selection of External Components<br>Electrical Specification:<br>Application Notes |            |  |

|     |                                             |                                                                                                                                        |            |  |

# **Chapter 5 - Power Control (POCO)**

| 5.1 | Overvi  | ew                                          | 5-1 |

|-----|---------|---------------------------------------------|-----|

| 5.2 | Archite | ecture                                      | 5-2 |

| 5.3 | Operat  | tional Description                          | 5-2 |

|     |         | System Reset/Power Up<br>Run Mode Operation |     |

|     | 5.3.3<br>5.3.4 | Standby Mode Clock Control Operation<br>Low Power Sleep Mode | 5-3 |

|-----|----------------|--------------------------------------------------------------|-----|

|     | 5.3.5          | Typical Configuration                                        | 5-4 |

| 5.4 | Program        | mmer's Model                                                 | 5-5 |

|     | 5.4.1          | Basic Register Operation                                     | 5-6 |

# **Chapter 6 - Programmable Peripheral Interface (PPI)**

| 6.1 | Overview 6                                                                                                                                | -1         |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 6.2 | Architecture 6                                                                                                                            | -1         |

| 6.3 | Operational Description 6                                                                                                                 | -2         |

| 6.4 | Programmer's Model 6                                                                                                                      | -4         |

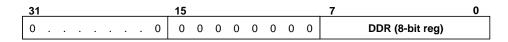

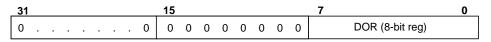

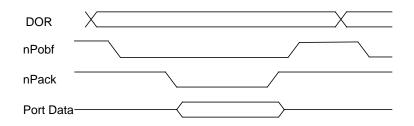

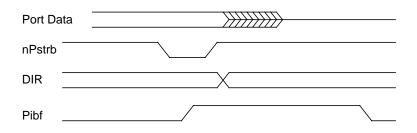

|     | 6.4.1Data Direction Register (DDR)66.4.2Data Input Register (DIR)66.4.3Data Output Register (DOR)66.4.4The Control Status Register (CSR)6 | 6-5<br>6-5 |

| 6.5 | Timing relationship diagrams 6                                                                                                            | -6         |

| 6.6 | External Interface                                                                                                                        | -8         |

# Chapter 7 - Memory/Peripheral Controller (MPC)

| 7.1 | Overview     |                                        |      |  |

|-----|--------------|----------------------------------------|------|--|

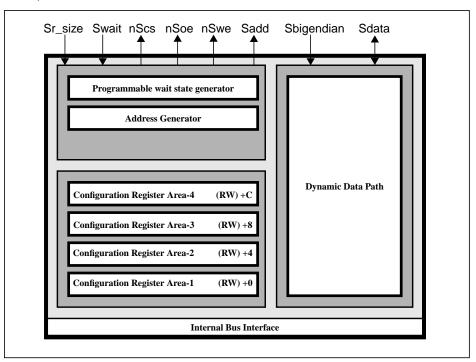

| 7.2 | Architecture |                                        |      |  |

| 7.3 | Opera        | Operational Description                |      |  |

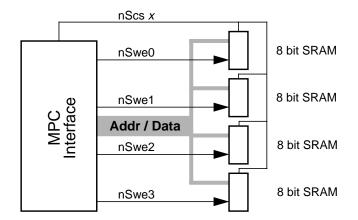

|     | 7.3.1        | Memory Areas                           | 7-3  |  |

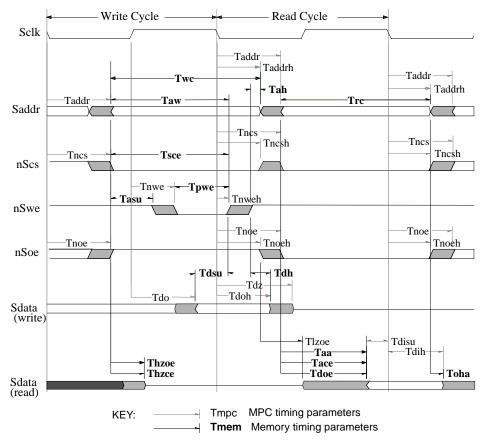

|     | 7.3.2        | Signal Relationships                   | 7-4  |  |

|     | 7.3.3        | Wait State Insertion                   | 7-5  |  |

|     | 7.3.4        | Instruction Fetches from Memory        | 7-8  |  |

|     | 7.3.5        | Data Transfers to and from Memory      | 7-10 |  |

|     | 7.3.6        | Endian configuration                   | 7-12 |  |

|     | 7.3.7        | Access to Non-Aligned Memory Addresses | 7-14 |  |

| 7.4 | Progra       | ammer's Model                          | 7-15 |  |

|     | 7.4.1        | MPC Configuration Registers            | 7-15 |  |

| 7.5 | Exterr       | nal Interfaces                         | 7-18 |  |

| 7.6        | Applica | ation Information: Designing a Memory System 7- | -19  |

|------------|---------|-------------------------------------------------|------|

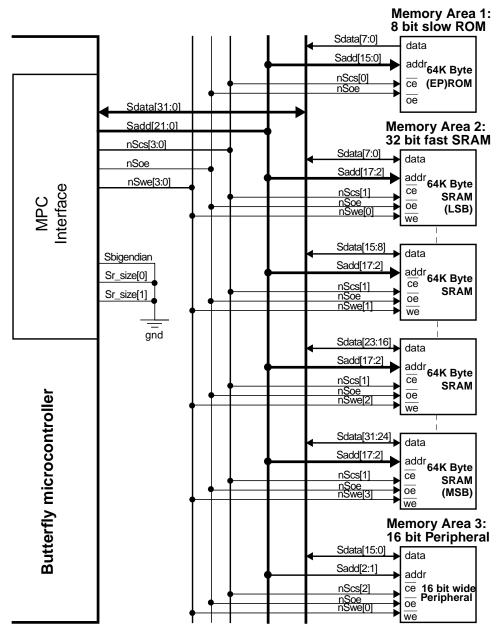

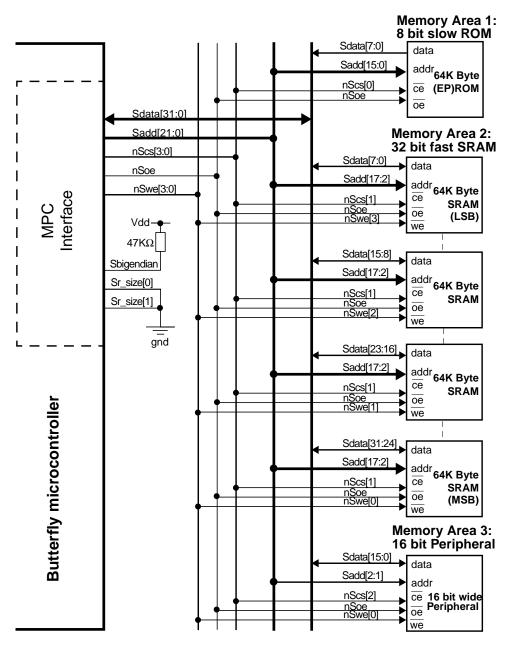

|            | 7.6.1   | Example system configuration7                   | '-19 |

|            | 7.6.2   | MPC Configuration Register Settings7            |      |

|            | 7.6.3   | Calculating Required Memory Timing Parameters7  | -23  |

| Chapter 8  | - Univ  | ersal Asynchronous Receiver/                    |      |

| Transmitte |         | -                                               |      |

|            | •       | •                                               | 0 4  |

| 8.1        | Overvie | ew 8                                            | 5- I |

| 8.2        | Operat  | tional Description                              | 8-3  |

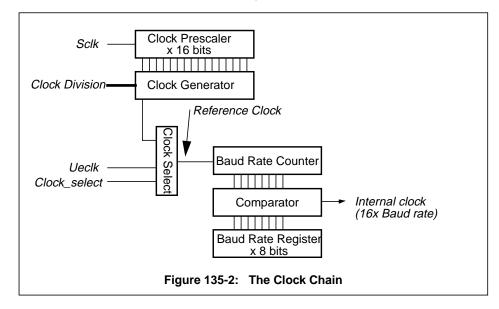

|            | 8.2.1   | Baud Rate Generation                            | 8-3  |

|            | 8.2.2   | Transmit Channel                                | 8-4  |

|            | 8.2.3   | Receive Channel                                 | 8-5  |

|            | 8.2.4   | Receive Data Filter                             |      |

|            | 8.2.5   | Data Transfer Methods                           |      |

|            | 8.2.6   | Manual Flow Control                             |      |

|            | 8.2.7   | Automatic Flow Control                          |      |

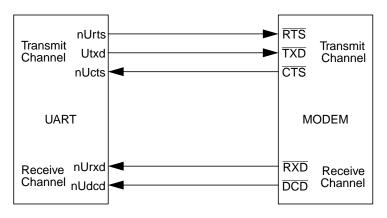

|            | 8.2.8   | Modem Flow Control                              |      |

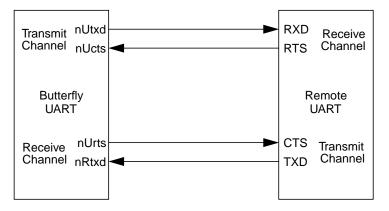

|            | 8.2.9   | Null Modem Flow Control 8                       | -10  |

| 8.3        | Progra  | mmer's Model 8-                                 | -11  |

|            | 8.3.1   | Register Descriptions 8                         | -12  |

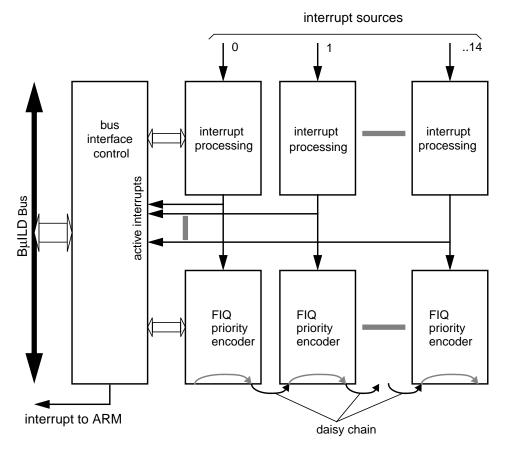

# Chapter 9 - Interrupt Controller (INTC)

| 9.1 | Introdu                                   | uction                                                                                                                       | 9-1 |

|-----|-------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|-----|

|     | 9.1.1                                     | Design Features                                                                                                              |     |

| 9.2 | Archite                                   | ecture                                                                                                                       | 9-2 |

| 9.3 | Opera                                     | tional Description                                                                                                           | 9-3 |

|     | 9.3.1<br>9.3.2<br>9.3.3<br>9.3.4<br>9.3.5 | Interrupt Controller Structure<br>Interrupt Processor<br>FIQ Priority Encoder<br>Bus Interface Control<br>External Interface |     |

| 9.4 | Progra                                    | ammer's Model                                                                                                                | 9-5 |

| 9.5 | Using                                     | the Interrupt Controller                                                                                                     | 9-6 |

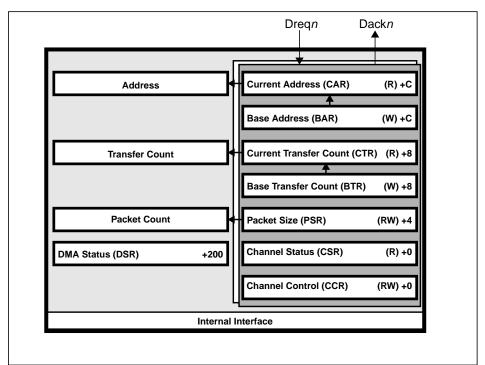

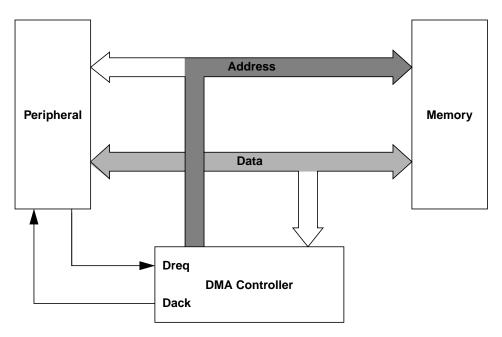

# Chapter 10 - DMA Controller (DMAC)

| 10.1 Overvi | ew                                 | 10-1  |

|-------------|------------------------------------|-------|

| 10.1.1      | DMA Controller Trigger Selection   | 10-2  |

| 10.2 Opera  | tional Description                 | 10-3  |

| 10.2.1      | Single Addressed (Fly-by) Transfer | 10-3  |

| 10.2.2      | Dual Addressed (Buffered) Transfer | 10-6  |

| 10.2.3      | Configuration                      | 10-10 |

| 10.3 Progra | mmer's Model                       | 10-13 |

| 10.3.1      | DMA Registers                      | 10-13 |

# Chapter 11 - Timer/Counter (TIC)

| 11.1 Overvi  | ew                              | 11-1 |

|--------------|---------------------------------|------|

| 11.1.1       | Design Features                 | 11-1 |

| 11.2 Archite | ecture                          | 11-2 |

| 11.3 Opera   | tional Description              | 11-2 |

| 11.3.1       | Prescaler Operation             | 11-3 |

| 11.3.2       | Halt on Zero (Mode 0)           |      |

| 11.3.3       | Free Running (Mode 1)           | 11-3 |

| 11.3.4       | Reload on Trigger (Mode 2)      | 11-4 |

| 11.3.5       | Pulse Width Modulation (Mode 3) | 11-4 |

| 11.4 Progra  | mmer's Model                    | 11-5 |

| 11.4.1       | Register Descriptions           | 11-5 |

# Chapter 12 - Watchdog Timer (WDOG)

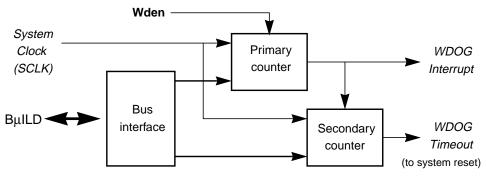

| 12.1 Overvi  | ew                                       | 12-1 |

|--------------|------------------------------------------|------|

| 12.1.1       | Design Features                          | 12-1 |

| 12.2 Archite | cture                                    | 12-1 |

| 12.3 Operat  | ional Description                        | 12-2 |

| 12.3.1       | Timer Operation and Watchdog Restart Key | 12-2 |

| 12.4 Progra  | mmer's Model                             | 12-3 |

| 12.4.1       | Control Register Format                  | 12-3 |

| 12.5 External Interface | 12-4 |

|-------------------------|------|

|-------------------------|------|

# **Appendix A - BmILD Bus Operation**

| A.1 Introduction |       | uction                                             | A-1 |

|------------------|-------|----------------------------------------------------|-----|

|                  | A.1.1 | Bus Masters                                        | A-1 |

|                  | A.1.2 | Bus Slaves                                         | A-2 |

|                  | A.1.3 | System Arbitration and Multiple Bus Master Support | A-2 |

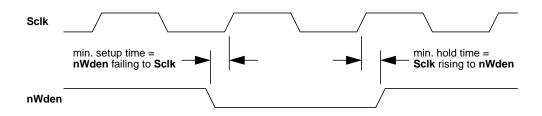

# **Appendix B - Physical and Electrical Specifications**

| B.1 | Device I/O Summary                      | B-1 |

|-----|-----------------------------------------|-----|

| B.2 | Pin Position Details                    | B-3 |

| B.3 | Package Options                         | B-5 |

| B.4 | Electrical performance Characteristics. | B-6 |

# **Appendix C - Further Information**

| C.1 | Related Documents | C-1 |

|-----|-------------------|-----|

| C.2 | Worldwide Offices | C-3 |

# Appendix D - PCB Layout Guidelines

| D.1 | Considerations regarding Power distribution | D-1 |

|-----|---------------------------------------------|-----|

| D.2 | Considerations regarding PCB track lengths  | D-2 |

# LIST OF FIGURES

### **Chapter 1 - Introduction**

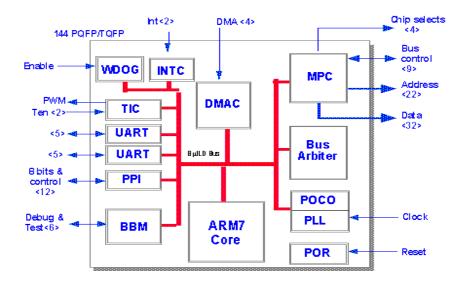

| Figure 1-1: Functional Block Diagram   | - BUTTERFLY 1-2 |

|----------------------------------------|-----------------|

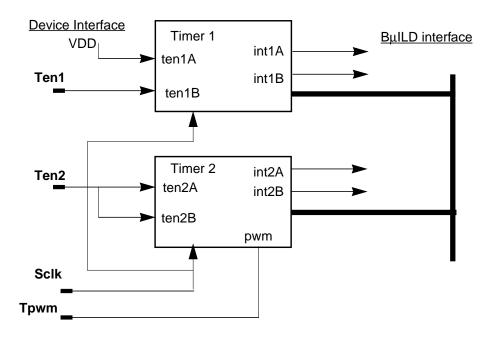

| Figure 1-3: Timer Counter connectivity | / 1-14          |

# Chapter 2 - ARM7 Microprocessor

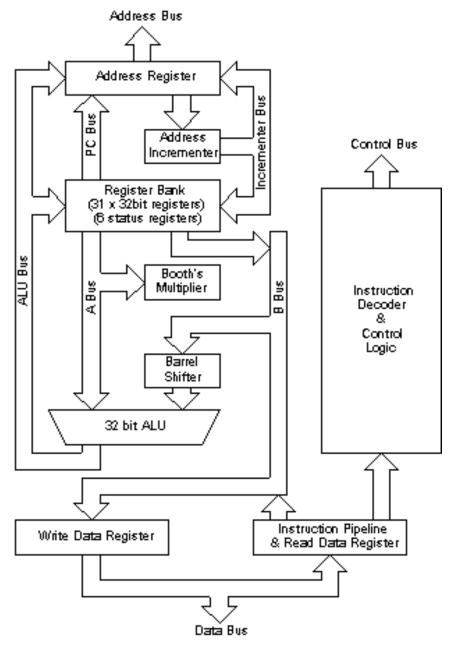

| Figure 2-1: ARM7 Architecture                             |      |

|-----------------------------------------------------------|------|

| Figure 2-2: Register Organisation                         | 2-5  |

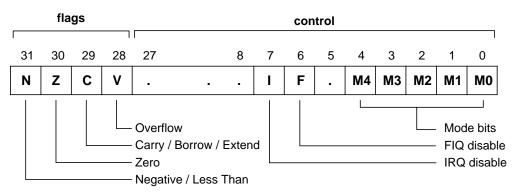

| Figure 2-3: Format of the Program Status Registers (PSRs) | 2-6  |

| Figure 2-4: Instruction Set Summary                       | 2-12 |

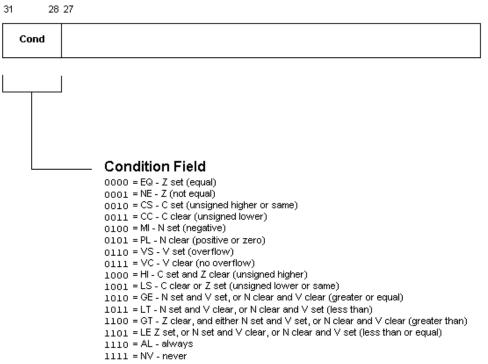

| Figure 2-5: Condition Codes                               |      |

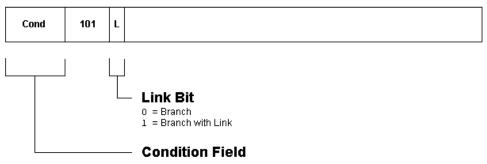

| Figure 2-6: Branch Instructions                           |      |

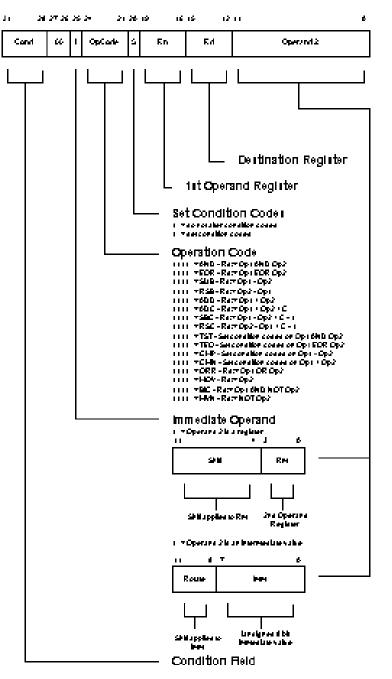

| Figure 2-7: Data Processing Instructions                  | 2-16 |

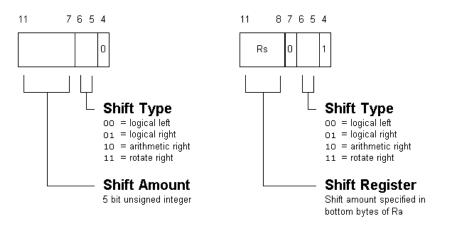

| Figure 2-8: ARM Shift Operations                          | 2-18 |

| Figure 2-9: Logical Shift Left                            | 2-19 |

| Figure 2-10: Logical Shift Right                          |      |

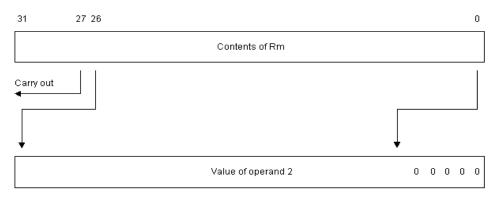

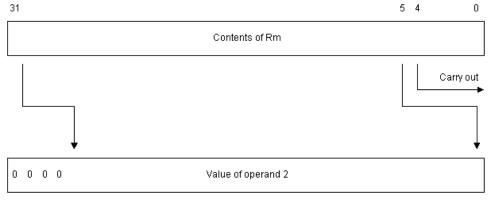

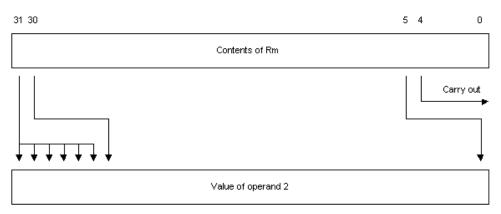

| Figure 2-11: Arithmetic Shift Right                       |      |

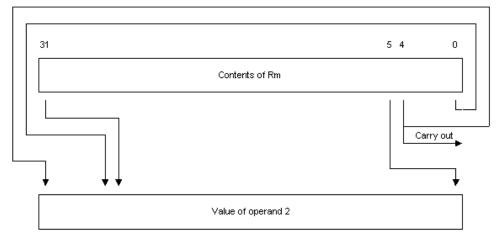

| Figure 2-12: Rotate Right                                 | 2-21 |

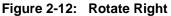

| Figure 2-13: Rotate Right Extended                        | 2-21 |

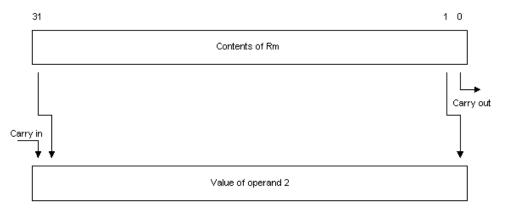

| Figure 2-14: PSR Transfer                                 | 2-28 |

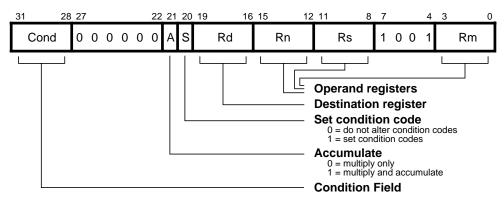

| Figure 2-15: Multiply Instructions                        |      |

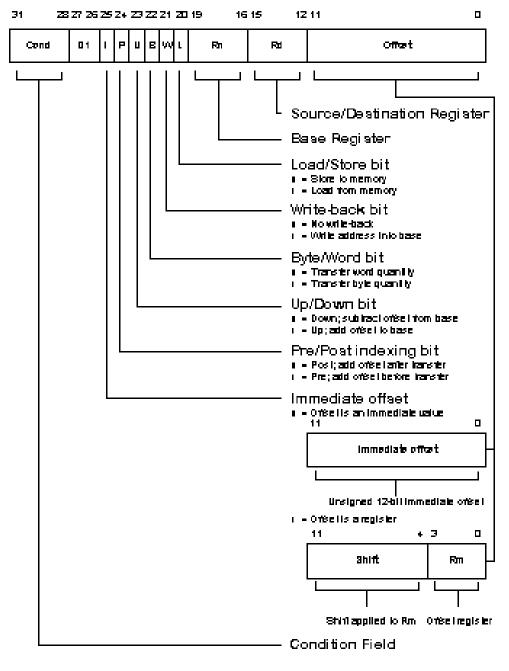

| Figure 2-16: Single Data Transfer Instructions            | 2-32 |

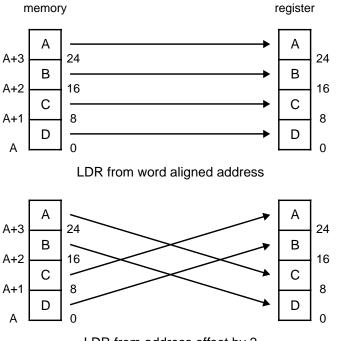

| Figure 2-17: Little Endian Offset Addressing              |      |

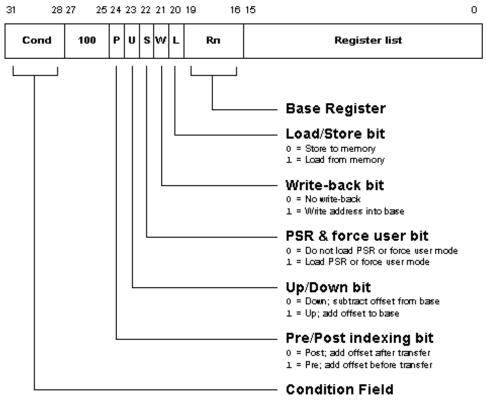

| Figure 2-18: Block Data Transfer Instructions             |      |

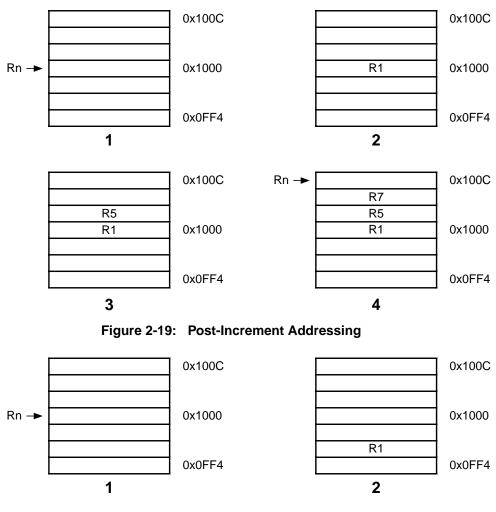

| Figure 2-19: Post-Increment Addressing                    |      |

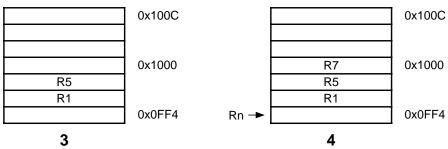

| Figure 2-20: Pre-Increment Addressing                     |      |

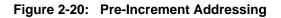

| Figure 2-21: Post-Decrement Addressing                    | 2-41 |

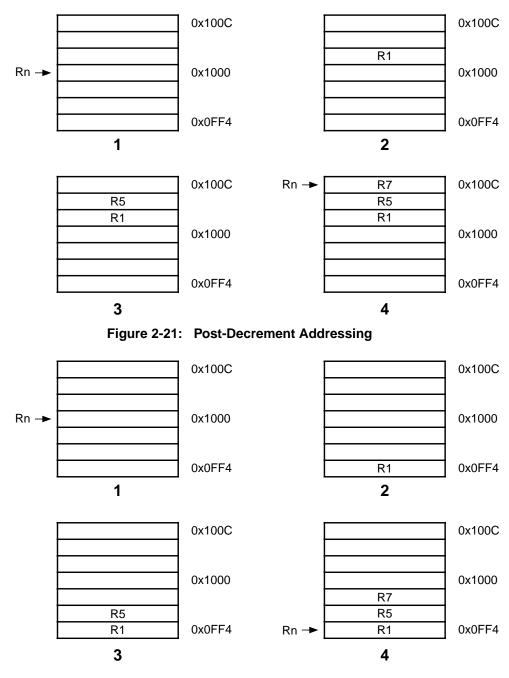

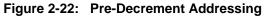

| Figure 2-22: Pre-Decrement Addressing                     | 2-41 |

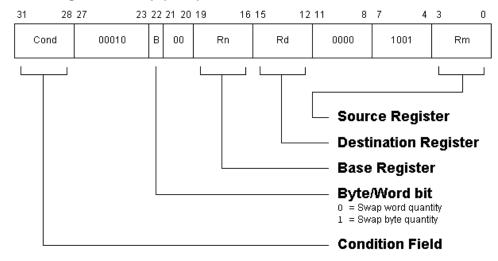

| Figure 2-23: Swap Instruction                             |      |

| Figure 2-24: Software Interrupt Instruction               |      |

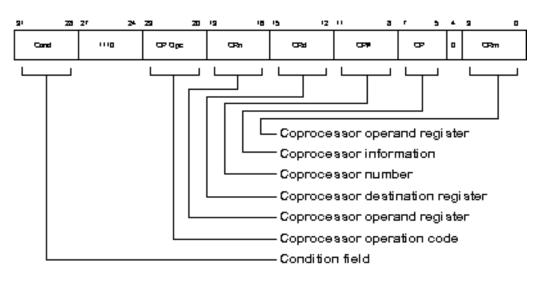

| Figure 2-25: Coprocessor Data Operation Instruction       | 2-50 |

| Figure 2-26: Undefined Instruction                        | 2-52 |

## Chapter 3 - Diagnostic Broadcast (BBM)

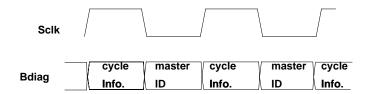

Figure 3-1: B ILD cycle and bus master details on 'Bdiag pins ...... 3-2

### Chapter 4 - Phase Locked Loop (PLL)

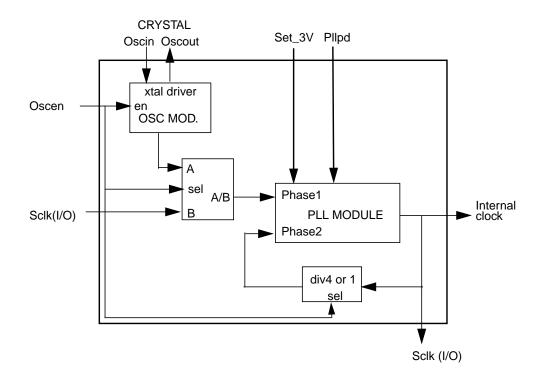

| Figure 4-1: Architecture                            | 4-2 |

|-----------------------------------------------------|-----|

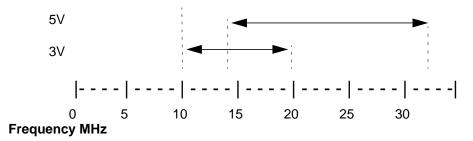

| Figure 4-2: PLL Operational ranges                  |     |

| Figure 4-3: PLL circuit for User supplied clock.    |     |

| Figure 4-4: PLL circuit for Crystal supplied clock. |     |

| Figure 4-5: PLL circuit for PLL bypass mode.        |     |

| Figure 4-6: External Components                     |     |

# Chapter 5 - Power Control (POCO)

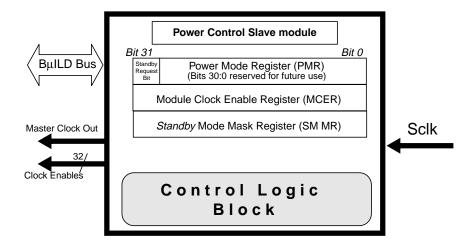

| Figure 5-1: Block Diagram of POCC | ) |

|-----------------------------------|---|

|-----------------------------------|---|

# Chapter 6 - Programmable Peripheral Interface (PPI)

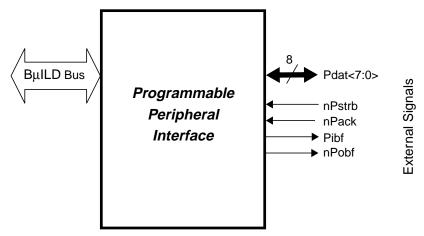

| Figure 6-1: PPI Module Block Diagram                 | . 6-1 |

|------------------------------------------------------|-------|

| Figure 6-2: Data Direction Register (Read/Write)     |       |

| Figure 6-3: Data Input Register (Read Only)          | . 6-5 |

| Figure 6-4: Data Output Register (Read/Write)        | . 6-5 |

| Figure 6-5: 8-Bit Port Control Status Register (CSR) | . 6-6 |

| Figure 6-6: Port Data Output (Modes 1 and 2)         | . 6-7 |

| Figure 6-7: Port Data Input (Modes 1 and 2)          | . 6-7 |

# Chapter 7 - Memory/Peripheral Controller (MPC)

| Figure 7-1: MPC Functional Blocks                                 | 7-2  |

|-------------------------------------------------------------------|------|

| Figure 7-2: MPC External Interface Signals                        |      |

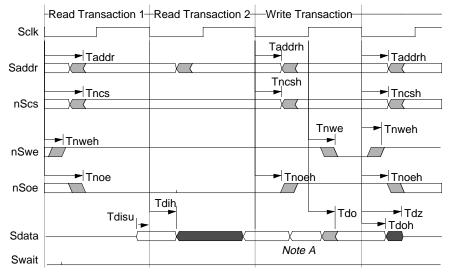

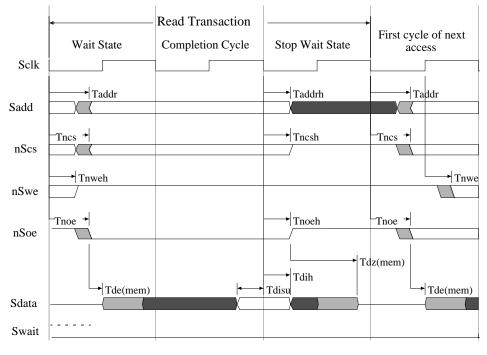

| Figure 7-3: Effect of Wait and Stop States on a Read Access       | 7-6  |

| Figure 7-4: MPC Externally Generated Wait State Insertion         | 7-8  |

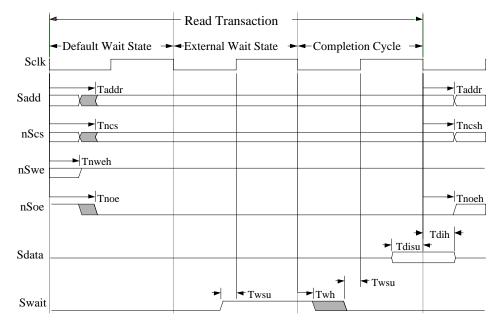

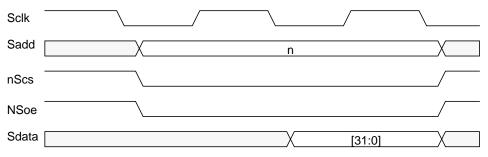

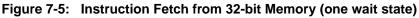

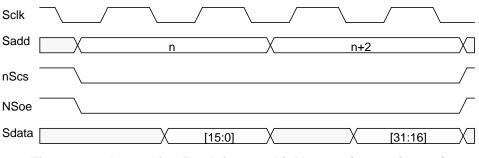

| Figure 7-5: Instruction Fetch from 32-bit Memory (one wait state) | 7-9  |

| Figure 7-6: Instruction Fetch from 16-bit Memory (one wait state) | 7-9  |

| Figure 7-7: Instruction Fetch from 8-bit Memory (one wait state)  | 7-10 |

| Figure 7-8: Writing to Individual Bytes of Memory                 | 7-12 |

| Figure 7-9: Little Endian addresses of bytes within words         | 7-13 |

| Figure 7-10: Big Endian addresses of bytes within words           | 7-13 |

| Figure 7-11: Single Register Slice                                | 7-15 |

| Figure 7-12: Configuration Register Reset State                   | 7-17 |

| Figure 7-13: Example Little-Endian System Configuration           | 7-20 |

| Figure 7-14: Example Big-Endian System Configuration              | 7-21 |

| Figure 7-15: Example MPC Configuration Register Settings          | 7-23 |

| Figure 7-16: Interfacing the MPC to SRAM                          | 7-24 |

|                                                                   |      |

#### Chapter 8 - Universal Asynchronous Receiver/Transmitter (UART)

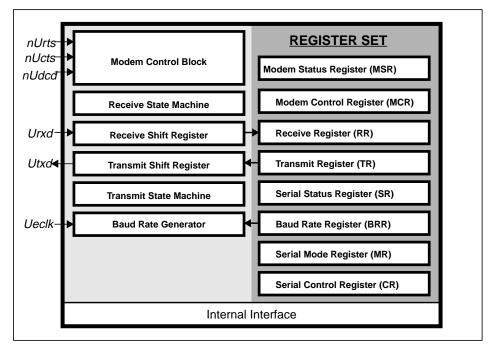

| Figure 8-1: Block Diagram                             | 8-2  |

|-------------------------------------------------------|------|

| Figure 8-2: The Clock Chain                           |      |

| Figure 8-3: Serial Transmission Example               | 8-4  |

| Figure 8-4: Receive data filter action                | 8-6  |

| Figure 8-5: Configuration 0 - Modem Flow Control      | 8-9  |

| Figure 8-6: Configuration 1 - Null modem Flow Control | 8-10 |

# Chapter 9 - Interrupt Controller (INTC)

| Figure 9-1: Interrupt Controller . |             | )-2 |

|------------------------------------|-------------|-----|

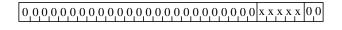

| Figure 9-2: FIQ Encoded Priority   | PRegister 9 | )-4 |

### Chapter 10 - DMA Controller (DMAC)

| Figure 10-1: Interface Diagram                         | 10-2 |

|--------------------------------------------------------|------|

| Figure 10-2: Architecture of Single-Addressed DMA      | 10-3 |

| Figure 10-3: Edge Triggered Block Transfer             | 10-4 |

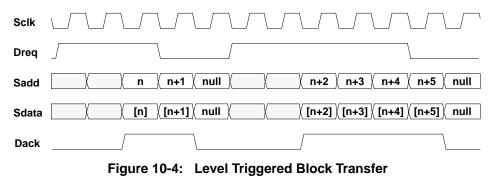

| Figure 10-4: Level Triggered Block Transfer            | 10-4 |

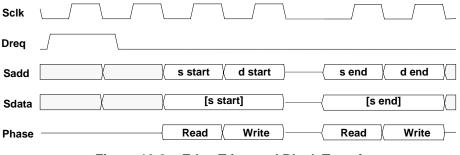

| Figure 10-5: Edge Triggered Packet Transfer (Size = 2) | 10-5 |

| Figure 10-6: Software Triggered Block Transfer         | 10-5 |

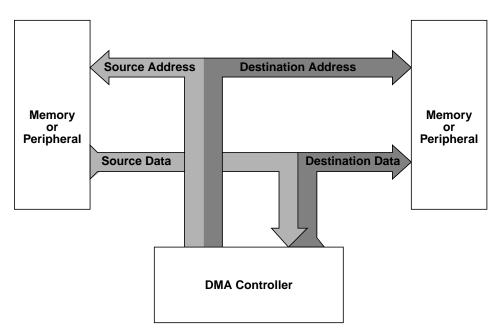

| Figure 10-7: Architecture of Dual Addressed DMA        | 10-6 |

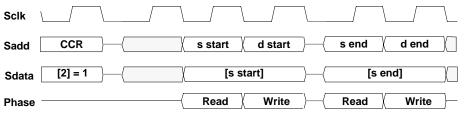

| Figure 10-8: Edge Triggered Block Transfer             | 10-7 |

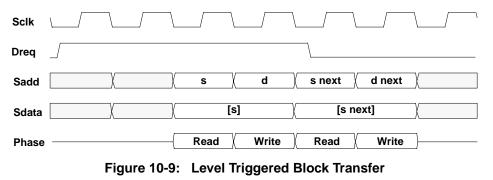

| Figure 10-9: Level Triggered Block Transfer            | 10-7 |

| Figure 10-10: Edge Triggered Packet Transfer           | 10-8 |

| Figure 10-11: Software Triggered Block Transfer        | 10-8 |

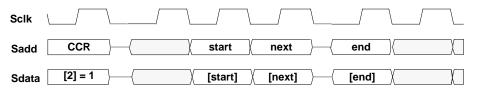

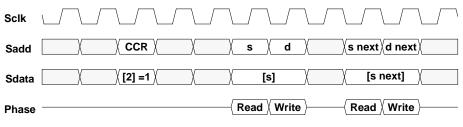

| Figure 10-12: Software Triggered Packet Transfer       | 10-9 |

|                                                        |      |

# Chapter 11 - Timer/Counter (TIC)

| Figure 11-1: Timer/Counter Architecture | . 11-2 |

|-----------------------------------------|--------|

| Figure 11-2: Control/Status Register    | . 11-6 |

### Chapter 12 - Watchdog Timer (WDOG)

| Figure 12-1: Watchdog Structure                         | 12-1 |

|---------------------------------------------------------|------|

| Figure 12-2: Control Register Format                    | 12-3 |

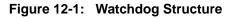

| Figure 12-3: Timing Relationship Between nWden and Sclk | 12-4 |

# **Appendix B - Physical and Electrical Specifications**

# LIST OF TABLES

# Chapter 1 - Introduction

| Table 1-1: Address Map                   | 1-6  |

|------------------------------------------|------|

| Table 1-2: Module Mapping                | 1-7  |

| Table 1-3: Priority Levels               | 1-9  |

| Table 1-4: Register View                 | 1-9  |

| Table 1-5: System Configuration Register | 1-10 |

| Table 1-6: DMAC Trigger Selection        | 1-11 |

| Table 1-7: Interrupt Source Channels     | 1-12 |

### Chapter 2 - ARM7 Microprocessor

| 2-6  |

|------|

| 2-10 |

| 2-17 |

| 2-44 |

| 2-54 |

| 2-56 |

| 2-57 |

| 2-58 |

| 2-59 |

| 2-60 |

| 2-61 |

| 2-62 |

| 2-63 |

| 2-64 |

| 2-65 |

| 2-65 |

| 2-66 |

|      |

### Chapter 3 - Diagnostic Broadcast (BBM)

| Table | 3-1: Encoding | of Bus Ma  | aster ID for | r Diagnostic Broad | Icast | 3-2 |

|-------|---------------|------------|--------------|--------------------|-------|-----|

| Table | 3-2: Encoding | of Cycle 7 | Type for Di  | agnostic Broadcas  | st    | 3-3 |

# Chapter 4 - Phase Locked Loop (PLL)

| Table 4-1: Signal definitions and Names      |  |

|----------------------------------------------|--|

| Table 4-2: Clock Modes                       |  |

| Table 4-3: Specification (3V and 5V nominal) |  |

| Table 4-4: Amplifier Specification: Vdd | =5V (nom) 4-12 |

|-----------------------------------------|----------------|

| Table 4-5: Amplifier Specification: Vdd | =3V(nom) 4-12  |

# Chapter 5 - Power Control (POCO)

| Table 5-1: Programmers Register View           | . 5- | -5 |

|------------------------------------------------|------|----|

| Table 5-2: Module Clock Enable Register (MCER) | . 5- | -5 |

### Chapter 6 - Programmable Peripheral Interface (PPI)

| Table 6-1: Programmers Register View                | 6-4 |

|-----------------------------------------------------|-----|

| Table 6-2: PPI Module External Pin List Description | 6-8 |

# Chapter 7 - Memory/Peripheral Controller (MPC)

| Table 7-1: Data Read from Memory                   | 7-11 |

|----------------------------------------------------|------|

| Table 7-2: Data Write to Memory                    | 7-12 |

| Table 7-3: Non-Aligned Address Accesses            | 7-14 |

| Table 7-4: Programmer's Register View              | 7-15 |

| Table 7-5: MPC nScs External Decode Map            | 7-15 |

| Table 7-6: Configuration Register Bit Actions      | 7-16 |

| Table 7-7: External Pin-Out Description            | 7-18 |

| Table 7-8: MPC Timing Parameters                   | 7-25 |

| Table 7-9: Typical SRAM Parameters (with formulae) | 7-26 |

|                                                    |      |

# Chapter 8 - Universal Asynchronous Receiver/Transmitter (UART)

| Table 8-1: Interface Description                                | 8-2  |

|-----------------------------------------------------------------|------|

| Table 8-2: Program Register View                                | 8-11 |

| Table 8-3: Serial Control Register (CR) - Read / Write, + 0x000 | 8-12 |

| Table 8-4: Serial Mode Register (MR) - Read / Write, + 0x004    | 8-13 |

| Table 8-5: Baud Rate Register (BRR) - Read / Write, + 0x008     | 8-13 |

| Table 8-6: Serial Status Register (SR) - Read, + 0x00C          | 8-14 |

| Table 8-7: Transmit Register (TR) - Write,+ 0x010               | 8-14 |

| Table 8-8: Receive Register (RR) - Read, + 0x010                | 8-15 |

| Table 8-9: Modem Control Register (MCR) - Read / Write,+0x 014  | 8-15 |

| Table 8-10: Modem Status Register - Read, + 0x01C               | 8-16 |

# Chapter 9 - Interrupt Controller (INTC)

# Chapter 10 - DMA Controller (DMAC)

| Table 10-1: DMA Controller Signals   10-2                                      |

|--------------------------------------------------------------------------------|

| Table 10-2: DMA Controller Registers         10-13                             |

| Table 10-3: DMA Controller Channel Registers 10-14                             |

| Table 10-4: Channel Control Register (CCR) - offset +0x0 10-15                 |

| Table 10-5: Channel Status Register (CSR) - offset +0x0 10-16                  |

| Table 10-6: Packet Size Register (PSR) - offset +0x4 10-17                     |

| Table 10-7: Transfer Count Registers - offset +0x8 10-17                       |

| Table 10-8: Address Registers - offset +0xC 10-18                              |

| Table 10-9: DMA Controller Status Register (DSR) - offset +0x200         10-18 |

| Chapter 11 - Timer/Counter (TIC)                                               |

| Table 11-1: Timer/Counter Address Map 11-5                                     |

| Table 11-2: Control/Status Register bit descriptions       11-6                |

| Chapter 12 - Watchdog Timer (WDOG)                                             |

| Table 12-1: Register Map    12-3                                               |

| Appendix B - Physical and Electrical Specifications                            |

| Table B-1: Device I/O SummaryB-1                                               |

| Appendix C - Further Information                                               |

| Table C-1: Related DocumentsC-1                                                |

# **Document Conventions**

- a. Numbers prefixed with '0x' are hexadecimal

- b. Register, flag and signal names are all in **bold** type

- c. External signal names begin with a Capital letter (which are prefixed with an "n" if active low), all internal signal names are in lower case.

- d. All active low signal names begin with an 'n'

- e. Bit positions within a Register Field are represented within square brackets [n]

- f. "Reserved": When associated with a register field, the location should not be written to, or read from. When used in a bit field amongst other referenced fields, the default value must be maintained during write operations.

- g. "Low", "clear": When associated with a signal or Bit field, refers to a logical condition 0.

- h. "High", "set": When associated with a signal or Bit field, refers to a logical condition 1

# **Chapter 1 - Introduction**

# 1.1 *BUTTERFLY* microcontroller overview

This book describes the *BUTTERFLY* microcontroller which is one of a range of products designed by Mitel to offer high performance processing whilst consuming very little power. This device is an entry level microcontroller targeted for emerging markets such as digital phones, set-top boxes and games where cost sensitivity is the utmost priority. The *BUTTERFLY* is object-code compatible with earlier ARM products and fully supported with industry standard cross development tools available on both PC and Sun platforms, including the ARM toolkit (from Mitel), a development board (MAP-1), and software routines for on-chip functions.

This is one of a series of integrated controllers designed around the BµILD (Bus for µController Integration in Low-power Designs) modular architecture. This on-chip 32-bit bus architecture has been developed to facilitate fully-testable, reliable and debuggable integrated processor products. The BµILD architecture means that Mitel can produce right-first-time complex Application Specific Standard Products (ASSP's) efficiently, meeting the fast time to market needs of customers in the emerging embedded processing markets.

*BUTTERFLY* is fabricated in 0.7µm CMOS technology and designed to operate at 25MHz (5 Volts) or 15MHz (3 Volts) over a commercial temperature range (0-70°C). At 5 Volts/25MHz, up to 22 MIPS (Dhrystone 2.1) of processing power is available and at 3 Volts/15MHz 13 MIPS is available.

#### 1.1.1 Features

*BUTTERFLY, available in a 144QFP package,* incorporates an ARM7 processor core, the industry's 32 bit processor leader in performance efficiency (MIPS/Watt), to which Mitel has added:

- Serial I/O

- Power management control circuitry

- A programmable memory interface

- support for 8,16 and 32-bit data transfers and memory widths

- Flexible address interface providing 4 memory areas, each of 4 Mbytes

- Flexible, 15 channel interrupt controller with programmable priority

- Watchdog Timer and four 32-bit timer/counters

- 8-bit wide Programmable Peripheral Interface (PPI)

- A Direct Memory Access (DMA) controller providing 2 fly-by channels or 1 memory channel

# 1.2 Functional Block Description

#### 1.2.1 BµILD Bus

This is a modular bus architecture and specification, via which all on-chip modules interface to each other. Such modules can either be bus masters or slaves. A bus master can initiate a bus access, generate addresses and control read or write transfers. A bus slave responds to a bus master request when selected by the system address decoder, and may, if required, assert a wait signal on the bus until the relevant data transfer has been completed. All internal data transfers on the BµILD bus are single cycle.

*BUTTERFLY* has three modules that are capable of operating as Bus masters. These are the ARM7 Core, DMAC and BBM, described below.

#### 1.2.2 ARM7 Processor (ARM7)

32-bit RISC processor core, object-code compatible with all ARM6 and ARM7 based products. The ARM7 is a fully static design and as such consumes dynamic power only when clocks are active.

# 1.2.3 BµILD Broadcast Module (BBM)

During application debugging, the BBM provides information about the activity on the internal B $\mu$ ILD bus, thus providing better observability of the device. It also holds the **System Configuration Register** and controls the bus mode (e.g. **RESET, ERROR, RUN** etc.).

### 1.2.4 Phase Locked Loop (PLL)

This balances the mark-space ratio of the incoming clock and reduces skew between clock and I/O signals, consequently improving set-up and hold margins of Data and Control signals. The PLL is also capable of deriving a highly stable system clock from a low cost off-chip crystal.

## 1.2.5 Power Control (POCO)

Each on-chip module has its own clock source network. The POCO permits any or all of these clock networks to be disabled under software control to minimise power consumption in any particular module. Other power control features can be found on certain on-chip functions to provide further power-management optimization. For example the processor can be put into "SLEEP" mode so that no CPU activity occurs until reactivated with an interrupt.

#### 1.2.6 Power-On Reset (POR)

This circuitry controls the hardware POR signal to ensure that all internal registers are set to a known state and all bus drivers are initialised to a tri-state condition at power-up. An external reset line is also provided.

### 1.2.7 Programmable Peripheral Interface (PPI)

8 I/O pins are provided which may be bit or byte addressed and configured in a latched or transparent mode. When in byte mode, buffer full/empty flags are available which can be used to generate an interrupt to the ARM7 processor.

# 1.2.8 Memory/Peripheral Controller (MPC)

The MPC ensures the correct multiplexing of data is applied for bus transfers between 8,16 or 32- bit on-chip or off-chip peripherals. Four different contiguous memory areas are available, each with an address range of 4Mbytes, with individually programmable wait and stop state generation. A "SWAP" function allows memory area "1", which is addressed at system reset, to be switched with memory area "4". This allows, for example, booting from ROM and then switching memory area 1 to address SRAM so that time-critical software and interrupt routines can operate from fast memory.

### 1.2.9 Universal Asynchronous Receiver Transmitter (UART)

Each full duplex asynchronous channel provides an RS232 type interface, which supports either a XON/XOFF software protocol, or hardware RTS/CTS handshake mechanism. The Receive and Transmit channels are double buffered. Each UART may be polled or use an interrupt scheme for BµILD bus transfers. An internal Baud rate generator can provide selectable data rates derived from on- or off-chip sources for an Rx/Tx pair. Directly triggered DMA transfers with the UART are also possible without the need for CPU intervention.

### 1.2.10 Interrupt Controller (INTC)

The ARM7 core accepts two types of interrupt: Normal (IRQ) and Fast (FIQ). All Interrupts on Butterfly can be switched between types, depending upon the relative priorities required.

The **INTC** is the central control logic that decodes the priority level and handles interrupt request signals from a total of 15 sources. External Interrupts can be set for edge or level sensitivity with a polarity option. To minimise interrupt latency, there is a hard-wired FIQ priority scheme for each channel, alternatively this can be ignored and the priority assessment handled in software.

### 1.2.11 DMA Controller (DMAC)

Two DMA engines are available on Butterfly. These may also be configured as a pair to provide a memory to memory DMA capability between any locations in the ARM7 memory space. Alternatively they may be used independently for Fly-by transfers between off-chip requestors and either on-chip or off-chip locations.

Single or multiple byte transfers (Demand or Burst Mode) are supported and may be word, half-word or byte wide.

# 1.2.12 Timer/Counters (TIC)

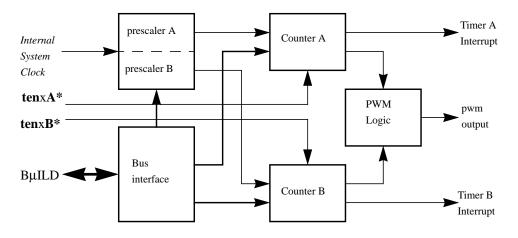

Four independent 32-bit timer/counters, each with an 8-bit prescaler capability are provided (Timers 1A, 1B, 2A and 2B). These are synchronous to the system clock and may be polled or set-up to generate interrupts on over-run and auto-reload. Timer 1A is permanently enabled. Timer 1B has an enable control input, Timers 2A and 2B, which both have enable inputs, can be configured as a pair to generate a PWM output that is connected to the PWM output pin.

### 1.2.13 Watchdog Timer (WDOG)

The function of the Watchdog Timer (WDOG) is to detect hardware lock-ups or run-time software errors. It performs this function by requiring the processor to write to one of its registers periodically. Should this not occur, the Watchdog will timeout and reset the system. This ensures that hardware/software lock-ups are recoverable.

# 1.3 BUTTERFLY System Details

#### 1.3.1 System Address Map

The system address map for the BUTTERFLY device is shown below in Table 1-1.

| Address Range            | Function                |

|--------------------------|-------------------------|

| 0x0000 0000 >> 003F FFFF | External-1:nScs0/nScs3# |

| 0x0040 0000 >> 1FFF FFFF | External-1 reflected*   |

| 0x2000 0000 >> 203F FFFF | External-2:nScs1        |

| 0x2040 0000 >> 3FFF FFFF | External-2 reflected*   |

| 0x4000 0000 >> 403F FFFF | External-3:nScs2        |

| 0x4040 0000 >> 5FFF FFFF | External-3 reflected*   |

| 0x6000 0000 >> 603F FFFF | External-4:nScs3/nScs0# |

| 0x6040 0000 >> 7FFF FFFF | External-4 reflected*   |

| 0x8000 0000 >> 9FFF FFFF | Reserved                |

| 0xA000 0000 >> BFFF FFFF | Reserved                |

| 0xC000 0000 >> DFFF FFFF | Reserved                |

| 0xE000 0000 >> E001 FFFF | Internal I/O            |

| 0xE002 0000 >> FFFF FFFF | Reserved                |

\* Reflected address areas will produce images of data in the original memory area addresses e.g. External-1 will repeat at addresses 0040 0000, 0080 0000, 00C0 0000 etc.

# See section 1.3.1.2 overleaf

#### Table 1-1: Address Map

The Internal I/O memory area is subdivided into 32 sub-regions extending from xE000 0000 to xE001 FFFF and assigned to the on-chip modules. Those modules capable of generating addresses are configured as 'bus masters' and the remaining modules as 'bus slaves'. The bus masters are:-

The ARM7 Processor

The BµILD Broadcast Module (BBM)

The DMA Controller

As only one bus master can be in control of the  $B\mu ILD$  bus at any one time, they are prioritised and given access to the bus in accordance with the arbitration system.

### 1.3.1.2 SWAP Function

The **System Configuration Register** (section 1.3.6) includes a control bit that swaps the address memory areas for chip selects **nScs0** and **nScs3**. This allows ROM devices to be used for ARM bootstrap code and then allow other memory (e.g. fast SRAM) to reside in low memory address locations (including those where exception vector tables reside), once the users application code is up and running. Note if **SWAP** is used, the set-up parameters for the relative external devices may also need reprogramming as described in section 7.6.2

#### 1.3.2 Address Map for internal I/O

Table 1-2 shows how registers for the System and individual modules are allocated memory areas within the Internal I/O memory space. Refer to the relevant chapter for further register descriptions.

Nb: Attempts to access an address that has no mapped register, or one that is designated as reserved, are likely to result in a run-time bus error.

| Address Range       | Function                             | Address Range             | Function               |

|---------------------|--------------------------------------|---------------------------|------------------------|

| 0xE000 0000- > 1FFF | Reserved                             | 0xE000 D000- > DFFF       | Reserved               |

| 0xE000 2000- > 2FFF | System Configuration (including BBM) | 0xE000 E000- > EFFF       | Timer 1                |

| 0xE000 3000- > 3FFF | Reserved                             | 0xE000 F000- > FFFF       | Timer 2                |

| 0xE000 4000- > 4FFF | Watchdog Timer                       | 0xE001 0000- > 1FFF       | Reserved               |

| 0xE000 5000- > 5FFF | Power Control                        | 0xE001 2000- > 2FFF       | PPI                    |

| 0xE000 6000- > 6FFF | Interrupt Controller                 | 0xE001 3000- > 7FFF       | Reserved               |

| 0xE000 7000- >7FFF  | Reserved                             | 0xE001 8000- > 8FFF       | UART 1                 |

| 0xE000 8000- > 8FFF | Memory/Peripheral<br>Controller      | 0xE001 9000- > 9FFF       | UART 2                 |

| 0xE000 9000- > BFFF | Reserved                             | 0xE001 A000- > AFFF       | Reserved<br>(Internal) |

| 0xE000 C000- > CFFF | DMA controller                       | 0xE001 B000><br>FFFF FFFF | Reserved               |

Table 1-2: Module Mapping

### 1.3.3 System Clock Control

Extensive control of the system clock distribution is provided by a Power Control (POCO) module. This provides both sleep and programmable standby modes. See Chapter 5 - Power Control (POCO) for more details.

#### 1.3.4 System Reset

The microcontroller system may be reset by a number of mechanisms:

- At power-up

- via an external reset pin **nSreset**

- via the watchdog timing out

In each case the initialization sequence is the same.

- The microcontroller enters **RESET** mode, resetting all internal modules, including the ARM CPU

- The ARM7 processor is granted the bus and proceeds to fetch its next instruction from address location 0x0000 0000.

- The MPC defaults to accessing external area 1 as slow memory (with 15 wait states and 15 stop states, and with a width defined by pins **Sr\_Size<1:0>**.

- Following successful Butterfly initialisation, the user should configure the MPC appropriate to the external devices connected to it.

**IMPORTANT NOTE:** Immediately after power-up and/or a rising edge of **nSreset**, **Sclk** should be clocked for at least 2 ARM **processor** cycles to bring the core into a stable state. If this is not performed then several mA can be consumed by the ARM core until these clocks have been provided.

### 1.3.5 System Bus Arbitration

The system contains three separate bus masters, (Modules capable of generating addresses), these being the ARM7 Processor, the DMA controller, and the B $\mu$ ILD Broadcast Module (BBM). The arbitration system uses a "highest priority" scheme. Bus masters request use of the Bus from the Arbiter. The highest priority bus master is granted the bus for as long as it wishes irrespective of the demands of lower priority bus masters. The priority levels implemented are as shown in Table 1-3

| Priority Level | Function |

|----------------|----------|

| 0- Highest     | BBM      |

| 1              | DMA      |

| 2- Lowest      | ARM7     |

Table 1-3: Priority Levels

The BBM block is primarily used for manufacturing test and system debug and hence requires the highest priority level, although it is not active during normal system operation. The ARM7 processor is bandwidth intensive, if not given the lowest priority then any lower priority master would rarely get access to the bus. A further feature allows the ARM to have priority on receipt of a FIQ interrupt. In this instance the ARM may be optionally promoted in priority to be above the DMA for the duration of any FIQ. Bit 1 in the **System Configuration Register** enables this function.

#### 1.3.6 System Configuration Register

After power-up, this register is should be initialised with suitable values for desired operation of the device. It also determines whether the Diagnostic broadcast facility is enabled or not.

| Address     | Register view                 | Function |

|-------------|-------------------------------|----------|

| 0xE000 2000 | Reserved (must remain '0')    | RW       |

| 0xE000 2004 | System Configuration Register | RW       |

Table 1-4: Register View

The System Configuration Register controls the operation of various system functions.

- The SWAP bit controls the operation of nScs0 and nScs3 as described in section 1.3.1

- Bit 1 controls the operation of the bus arbitration unit as described in section 1.3.5

- Bit 2 is reserved

- Bits 3-5 control the selection of the DMA request input to the DMA controller described in Chapter 10 - DMA Controller (DMAC)

- Bits 6-7 select the UART's to work in either external clock (1) or DCD (0) mode.

- Bits 8-31 are reserved and should be programmed to 0.

| Bit  | Function                                          | Reset<br>Value |

|------|---------------------------------------------------|----------------|

| 0    | SWAP [1] swaps external nScs0 and nScs3 addresses | 0              |

| 1    | Arbitration ARM (FIQ mode) promote                | 0              |

| 2    | Reserved (must be 0)                              | 0              |

| 3-5  | DMA mux-1 channel select: see below               | 0              |

| 6    | UART1 [1] external clock / [0] nDCD enable pin    | 0              |

| 7    | UART2 [1] external clock / [0] nDCD enable pin    | 0              |

| 8-31 | Reserved (must be 0)                              | 0              |

# Table 1-5: System Configuration Register

# 1.3.7 DMA

The following table describes the encoding system for allocating DMA channels to sources that have a DMA capability. More details can be found in Chapter 10 - DMA Controller (DMAC)

| Channel Select<br>System<br>Configuration Register |       |       | Source Channel       |

|----------------------------------------------------|-------|-------|----------------------|

| Bit 5                                              | Bit 4 | Bit 3 |                      |

| 0                                                  | 0     | 0     | External Dreq-1      |

| 0                                                  | 0     | 1     | UART 2 Receive       |

| 0                                                  | 1     | 0     | PPI 1 IBF            |

| 0                                                  | 1     | 1     | UART 1 Receive       |

| 1                                                  | 0     | 0     | External Interrupt-1 |

| 1                                                  | 0     | 1     | UART 2 Transmit      |

| 1                                                  | 1     | 0     | PPI 1 OBE            |

| 1                                                  | 1     | 1     | UART 1 transmit      |

Table 1-6: DMAC Trigger Selection

The following is the channel allocation number for each Bµild module. More information on interrupt control may be found in Chapter 9 - Interrupt Controller (INTC).

| Channel                 | Interrupt Source     | Function     |

|-------------------------|----------------------|--------------|

| 0<br>(highest priority) | WDOG                 | "Bark"       |

| 1                       | Reserved             |              |

| 2                       | Reserved             |              |

| 3                       | DMAC                 |              |

| 4                       | Reserved             |              |

| 5                       | Reserved             |              |

| 6                       | TIC1                 | Time out A   |

| 7                       | TIC1                 | Time out B   |

| 8                       | External Interrupt 1 | User defined |

| 9                       | Reserved             |              |

| 10                      | Reserved             |              |

| 11                      | PPI                  | IBF          |

| 12                      | PPI                  | OBE          |

| 13                      | Reserved             |              |

| 14                      | UART 1               | Error        |

| 15                      | UART 1               | RBF          |

| 16                      | UART 1               | TBE          |

| 17                      | Reserved             |              |

| 18                      | TIC2                 | Time out A   |

| 19                      | TIC2                 | Time out B   |

| 20                      | External Interrupt 2 | User defined |

| 21                      | Reserved             |              |

| 22                      | Reserved             |              |

| 23                      | Reserved             |              |

Table 1-7: Interrupt Source Channels

| Channel             | Interrupt Source | Function |

|---------------------|------------------|----------|

| 24                  | Reserved         |          |

| 25                  | Reserved         |          |

| 26                  | UART 2           | Error    |

| 27                  | UART 2           | RBF      |

| 28                  | UART 2           | TBE      |

| 29                  | Reserved         |          |

| 30                  | Reserved         |          |

| 31(lowest priority) | Reserved         |          |

Table 1-7: Interrupt Source Channels (Continued)

The four timer interrupts (channels 6, 7, 18, and 19) are edge triggered. All other internally generated interrupt sources are level sensitive, active *HIGH*.

Directly driven external interrupts are user defined, and can be set up for either Edge or Level sensitivity. For these, the edge/level and polarity registers need to be set up to match the required operation. The values that need to be written are:

| edge/level | 0x000C00C0<br>0x001C01C0 | external interrupts are level sensitive external interrupts are edge sensitive |

|------------|--------------------------|--------------------------------------------------------------------------------|

| polarity   | 0xFFFFFFFF               | external interrupts are active high or<br>rising edge triggered                |

|            | 0xFFEFFEFF               | external interrupts are active low or<br>falling edge triggered                |

## 1.3.9 Timer Counter (TIC) configuration

Figure 1-3: Timer Counter connectivity

Timer Counters "1" and "2" are connected as shown in Figure 1-3: Timer Counter connectivity. Please refer to Chapter 11 - Timer/Counter (TIC) for more details

# Chapter 2 - ARM7 Microprocessor

# 2.1 Overview

The ARM7 is part of the Advanced RISC Machines (ARM) family of general purpose 32bit microprocessors, which offer very low power consumption and low price for high performance devices. The architecture is based on Reduced Instruction Set Computer (RISC) principles, and the instruction set and related decode mechanism are much simpler in comparison with microprogrammed Complex Instruction Set Computers. This results in a high instruction throughput and impressive real-time interrupt response from a small and cost-effective chip.

The instruction set comprises eleven basic instruction types:

- Two of these make use of the on-chip arithmetic logic unit, barrel shifter and multiplier to perform high-speed operations on the data in a bank of 31 registers, each 32 bits wide;

- Three classes of instruction control data transfer between memory and the registers, one

optimised for flexibility of addressing, another for rapid context switching and the third for

swapping data;

- Three instructions control the flow and privilege level of execution; and

- Three types are dedicated to the control of external coprocessors which allow the functionality of the instruction set to be extended in an open and uniform way.

The ARM instruction set is a good target for compilers of many different high-level languages. Where required for critical code segments, assembly code programming is also straightforward, unlike some RISC processors which depend on sophisticated compiler technology to manage complicated instruction interdependencies.

Pipelining is employed so that all parts of the processing and memory systems can operate continuously. Typically, while one instruction is being executed, its successor is being decoded, and a third instruction is being fetched from memory.

ARM7 is a fully static CMOS implementation of the ARM which allows the clock to be stopped in any part of the cycle with extremely low residual power consumption and no loss of state.

# 2.2 Architecture

Figure 2-1: ARM7 Architecture

# 2.3 Programmer's Model

ARM7 supports a variety of operating configurations. One is controlled by an input and is known as the *hardware configuration*. Others may be controlled by software and these are known as *operating modes*. On Butterfly's internal Bµild bus, the ARM7's lowest BIGEND control bit, which determines whether the lowest addressed byte is least of most significant in a multi-byte word, is set (i.e. Little Endian). However for off-chip accesses, this may be programmed through the MPC using the Sbigendian pin. Please see Chapter 6 for further information.

## 2.3.1 Operating Mode Selection

ARM7 has a 32 bit data bus and a 32 bit address bus. The data types the processor supports are Bytes (8 bits) and Words (32 bits), where words must be aligned to four byte boundaries. Instructions are exactly one word, and data operations (e.g. ADD) are only performed on word quantities. Load and store operations can transfer either bytes or words.

ARM7 supports six modes of operation:

- [1] User mode (usr): the normal program execution state

- [2] FIQ mode (fiq): designed to support a data transfer or channel process

- [3] IRQ mode (irq): used for general purpose interrupt handling

- [4] Supervisor mode (svc): a protected mode for the operating system

- [5] Abort mode (abt): entered after a data or instruction prefetch abort

- [6] Undefined mode (und): entered when an undefined instruction is executed

Mode changes may be made under software control or may be brought about by external interrupts or exception processing. Most application programs will execute in User mode. The other modes, known as *privileged modes*, will be entered to service interrupts or exceptions or to access protected resources.

## 2.3.2 Registers

The processor has a total of 37 registers made up of 31 general 32 bit registers and 6 status registers. At any one time 16 general registers (R0 to R15) and one or two status registers are visible to the programmer. The visible registers depend on the processor mode and the other registers (the *banked registers*) are switched in to support IRQ, FIQ, Supervisor, Abort and Undefined mode processing. The register bank organisation is shown in *Figure 2-2: Register Organisation*. The banked registers are shaded in the diagram.

In all modes 16 registers, R0 to R15, are directly accessible. All registers except R15 are general purpose and may be used to hold data or address values. Register R15 holds the Program Counter (PC). When R15 is read, bits [1:0] are zero and bits [31:2] contain the PC. A seventeenth register (the CPSR - Current Program Status Register) is also accessible. It contains condition code flags and the current mode bits and may be thought of as an extension to the PC.

R14 is used as the subroutine link register and receives a copy of R15 when a Branch and Link instruction is executed. It may be treated as a general purpose register at all other times. R14\_svc, R14\_irq, R14\_fiq, R14\_abt and R14\_und are used similarly to hold the return values of R15 when interrupts and exceptions arise, or when Branch and Link instructions are executed within interrupt or exception routines.

FIQ mode has seven banked registers mapped to R8-14 (R8\_fiq-R14\_fiq). Many FIQ programs will not need to save any registers. User mode, IRQ mode, Supervisor mode, Abort mode and Undefined mode each have two banked registers mapped to R13 and R14. The two banked registers allow these modes to each have a private stack pointer and link register. Supervisor, IRQ, Abort and Undefined mode programs which require more than these two banked registers are expected to save some or all of the caller's registers (R0 to R12) on their respective stacks. They are then free to use these registers which they will restore before returning to the caller. In addition there are also five SPSRs (Saved Program Status Registers) which are loaded with the CPSR when an exception occurs. There is one SPSR for each privileged mode.

| User32   | FIQ32    | Supervisor32 | Abort32  | IRQ32    | Undefined32 |

|----------|----------|--------------|----------|----------|-------------|

| R0       | R0       | R0           | R0       | R0       | R0          |

| R1       | R1       | R1           | R1       | R1       | R1          |

| R2       | R2       | R2           | R2       | R2       | R2          |

| R3       | R3       | R3           | R3       | R3       | R3          |

| R4       | R4       | R4           | R4       | R4       | R4          |

| R5       | R5       | R5           | R5       | R5       | R5          |

| R6       | R6       | R6           | R6       | R6       | R6          |

| R7       | R7       | R7           | R7       | R7       | R7          |

| R8       | R8_fiq   | R8           | R8       | R8       | R8          |

| R9       | R9_fiq   | R9           | R9       | R9       | R9          |

| R10      | R10_fiq  | R10          | R10      | R10      | R10         |

| R11      | R11_fiq  | R11          | R11      | R11      | R11         |

| R12      | R12_fiq  | R12          | R12      | R12      | R12         |

| R13      | R13_fiq  | R13_svc      | R13_abt  | R13_irq  | R13_und     |

| R14      | R14_fiq  | R14_svc      | R14_abt  | R14_irq  | R14_und     |

| R15 (PC) | R15 (PC) | R15 (PC)     | R15 (PC) | R15 (PC) | R15 (PC)    |

# General Registers and Program Counter Modes

# **Program Status Registers**

## Figure 2-2: Register Organisation

The format of the Program Status Registers is shown in *Figure 2-3: Format of the Program Status Registers (PSRs)*. The N, Z, C and V bits are the *condition code flags*. The condition code flags in the CPSR may be changed as a result of arithmetic and logical operations in the processor and may be tested by all instructions to determine if the instruction is to be executed.

Figure 2-3: Format of the Program Status Registers (PSRs)

The I and F bits are the *interrupt disable bits.* The I bit disables IRQ interrupts when it is set and the F bit disables FIQ interrupts when it is set. The M0, M1, M2, M3 and M4 bits (M[4:0]) are the *mode bits*, and these determine the mode in which the processor operates. The interpretation of the mode bits is shown in *Table 2-1: The Mode Bits.* Not all combinations of the mode bits define a valid processor mode. Only those explicitly described shall be used.

The bottom 28 bits of a PSR (incorporating I, F and M[4:0]) are known collectively as the *control bits*. The control bits will change when an exception arises and in addition can be manipulated by software when the processor is in a privileged mode. Unused bits in the PSRs are reserved and their state shall be preserved when changing the flag or control bits. Programs shall not rely on specific values from the reserved bits when checking the PSR status, since they may read as one or zero in future processors.

| M[4:0] | Mode       | Accessible register set  |                |  |  |

|--------|------------|--------------------------|----------------|--|--|

| 10000  | User       | PC,R14R0                 | CPSR           |  |  |

| 10001  | FIQ        | PC,R14_fiqR8_fiq,R7R0    | CPSR, SPSR_fiq |  |  |

| 10010  | IRQ        | PC,R14_irqR13_irq,R12R0  | CPSR, SPSR_irq |  |  |

| 10011  | Supervisor | PC,R14_svcR13_svc,R12R0  | CPSR, SPSR_svc |  |  |

| 10111  | Abort      | PC,R14_abtR13_abt,R12R0  | CPSR, SPSR_abt |  |  |

| 11011  | Undefined  | PC,R14_undR13_und, R12R0 | CPSR, SPSR_und |  |  |

Table 2-1: The Mode Bits

## 2.3.3 Exceptions

Exceptions arise whenever there is a need for the normal flow of program execution to be broken, so that (for example) the processor can be diverted to handle an interrupt from a peripheral. The processor state just prior to handling the exception must be preserved so that the original program can be resumed when the exception routine has completed. Many exceptions may arise at the same time.

ARM7 handles exceptions by making use of the banked registers to save state. The old PC and CPSR contents are copied into the appropriate R14 and SPSR and the PC and mode bits in the CPSR bits are forced to a value which depends on the exception. Interrupt disable flags are set where required to prevent otherwise unmanageable nestings of exceptions. In the case of a re-entrant interrupt handler, R14 and the SPSR should be saved onto a stack in main memory before re-enabling the interrupt; when transferring the SPSR register to and from a stack, it is important to transfer the whole 32 bit value, and not just the flag or control fields. When multiple exceptions arise simultaneously, a fixed priority determines the order in which they are handled. The priorities are listed later in this chapter.

In Butterfly, all interrupts are controlled by the Interrupt Controller described in Chapter 8. This provides the capability of multiple interrupt source channels.

## 2.3.4 FIQ

The FIQ (Fast Interrupt reQuest) exception is externally generated by taking the **nFIQ** input LOW. This input can accept asynchronous transitions, and is delayed by one clock cycle for synchronisation before it can affect the processor execution flow. It is designed to support a data transfer or channel process, and has sufficient private registers to remove the need for register saving in such applications (thus minimising the overhead of context switching). The FIQ exception may be disabled by setting the F flag in the CPSR (but note that this is not possible from User mode). If the F flag is reset, ARM7 checks for a LOW level on the output of the FIQ synchroniser at the end of each instruction.

When a FIQ is detected, ARM7 performs the following:

- Saves the address of the next instruction to be executed plus 4 in R14\_fiq; saves CPSR in SPSR\_fiq

- [2] Forces M[4:0]=10001 (FIQ mode) and sets the F and I bits in the CPSR

- [3] Forces the PC to fetch the next instruction from address 0x1C

To return normally from FIQ, use SUBS PC, R14\_fiq,#4 which will restore both the PC (from R14) and the CPSR (from SPSR\_fiq) and resume execution of the interrupted code.

## 2.3.5 IRQ

The IRQ (Interrupt ReQuest) exception is a normal interrupt caused by a LOW level on the **nIRQ** input. It has a lower priority than FIQ, and is masked out when a FIQ sequence is entered. Its effect may be masked out at any time by setting the I bit in the CPSR (but note that this is not possible from User mode). If the I flag is reset, ARM7 checks for a LOW level on the output of the IRQ synchroniser at the end of each instruction. When an IRQ is detected, ARM7 performs the following:

- Saves the address of the next instruction to be executed plus 4 in R14\_irq; saves CPSR in SPSR\_irq

- [2] Forces M[4:0]=10010 (IRQ mode) and sets the I bit in the CPSR

- [3] Forces the PC to fetch the next instruction from address 0x18

To return normally from IRQ, use SUBS PC,R14\_irq,#4 which will restore both the PC and the CPSR and resume execution of the interrupted code.

## 2.3.6 Abort

An ABORT can be signalled by the external **ABORT** input. ABORT indicates that the current memory access cannot be completed. For instance, in a virtual memory system the data corresponding to the current address may have been moved out of memory onto a disc, and considerable processor activity may be required to recover the data before the access can be performed successfully. ARM7 checks for ABORT during memory access cycles. When successfully aborted ARM7 will respond in one of two ways:

- [1] If the abort occurred during an instruction prefetch (a *Prefetch Abort*), the pre-fetched instruction is marked as invalid but the abort exception does not occur immediately. If the instruction is not executed, for example as a result of a branch being taken while it is in the pipeline, no abort will occur. An abort will take place if the instruction reaches the head of the pipeline and is about to be executed.

- [2] If the abort occurred during a data access (a *Data Abort*), the action depends on the instruction type.

- [a] Single data transfer instructions (LDR, STR) will write back modified base registers and the Abort handler must be aware of this.

- [b] The swap instruction (SWP) is aborted as though it had not executed, though externally the read access may take place.

- [c] Block data transfer instructions (LDM, STM) complete, and if write-back is set, the base is updated. If the instruction would normally have over-written the base with data (i.e. LDM with the base in the transfer list), this over-writing is

prevented. All register over-writing is prevented after the Abort is indicated, which means in particular that R15 (which is always last to be transferred) is preserved in an aborted LDM instruction.

When either a prefetch or data abort occurs, ARM7 performs the following:

- [1] Saves the address of the aborted instruction plus 4 (for prefetch aborts) or 8 (for data aborts) in R14\_abt; saves CPSR in SPSR\_abt.

- [2] Forces M[4:0]=10111 (Abort mode) and sets the I bit in the CPSR.

- [3] Forces the PC to fetch the next instruction from either address 0x0C (prefetch abort) or address 0x10 (data abort).

To return after fixing the reason for the abort, use SUBS PC,R14\_abt,#4 (for a prefetch abort) or SUBS PC,R14\_abt,#8 (for a data abort). This will restore both the PC and the CPSR and retry the aborted instruction.